# L5953

## MULTIPLE SWITCHING VOLTAGE REGULATOR

#### PRODUCT PREVIEW

- PWM: ADJUSTABLE 2.5/10V 1A SWITCHING VOLTAGE REGULATOR

- EXTERNAL POWER MOS ABILITY FOR OUTPUT CURRENT ENHANCEMENT

- SYNCHRONIZATION FUNCTION

- REG1- LINEAR LOW DROP 3.3/5V 250mA STBY VOLTAGE REGULATOR (LOW CURRENT CONSUMPTION) with RESET

- REG2- LINEAR VOLTAGE REGULATOR 1.5V to 3.3V EXTERNALLY ADJUSTABLE - 300mA MAXIMUM CURRENT

- HSD1 : 500mA HIGH SIDE DRIVER

- HSD2 : 200mA HIGH SIDE DRIVER

- SPI INTERFACE

- SPI DIAGNOSTICS HSD1, HSD2

- DOUBLE SWITCHING FREQUENCY SPI SELECTABLE

- DOUBLE INPUT LVW

#### **SPI FUNCTIONS**

- INPUT CONTROLS

- Turn-on/off PWM

- Turn-on/off REG2

- Turn-on/off HSD1

- Turn-on/off HSD2

- Switching frequency selection f1- f2

- OUTPUT FUNCTIONS:

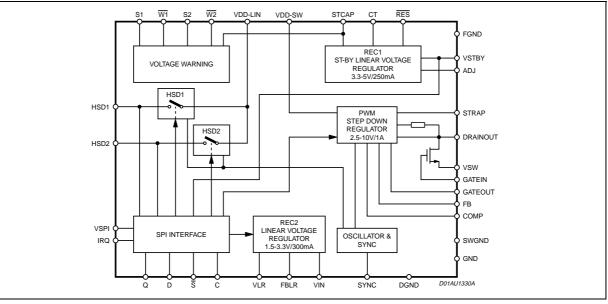

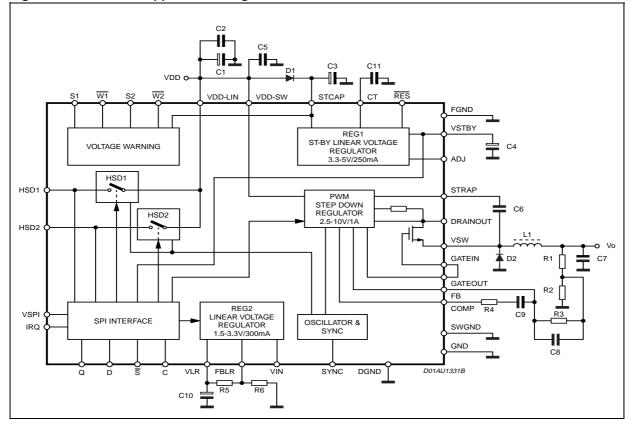

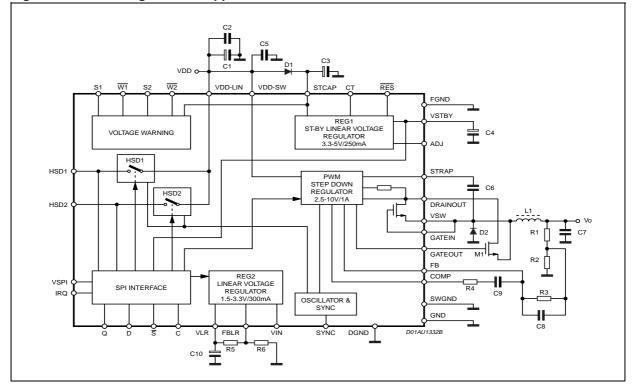

## **BLOCK DIAGRAM**

- HSD1 & HSD2 short to gnd, open load and short to battery (Test mode)

- Thermal warning

#### PROTECTIONS

- OVERVOLTAGE PROTECTION

- INTERNAL CURRENT LIMITING

- THERMAL SHUTDOWN

- ESD

#### DESCRIPTION

The L5953 is the integration of one switching regulator, two linear voltage regulators, two low voltage warnings and two high side drivers. It has a stand-by operation mode (low current consumption) where only the stand-by voltage regulator plus the low voltage warnings are active. The other regulators and high side drivers are controlled by the SPI interface.

September 2003

This is preliminary information on a new product now in development. Details are subject to change without notice.

## L5953

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol             | Parameter                                                           | Value              | Unit |

|--------------------|---------------------------------------------------------------------|--------------------|------|

| V <sub>DD</sub>    | DC Operating Supply Voltage                                         | -0.6 to 30         | V    |

|                    | Transient Supply Overvoltage (250ms)                                | 50                 | V    |

| V <sub>SPI</sub>   | Supply Voltage for SPI I/O                                          | -0.6 to 6          | V    |

| lo                 | Voltage Regulator Output Current                                    | Internally limited |      |

| V <sub>inlog</sub> | Input Voltage (C,D,Q,S,SYNC)                                        | 0 to 6             | V    |

| RESR               | Output Capacitor Series Eq. Resistance (Linear reg.)(Allowed range) | From 0.2 to 10     | Ω    |

| T <sub>op</sub>    | Operating Temperature Range                                         | -40 to 85          | °C   |

| T <sub>stg</sub>   | Storage Temperature Ranges                                          | -55 to 150         | °C   |

| Тj                 | Operative Junction Temperature                                      | -40 to 150         | °C   |

## THERMAL DATA

| Symbol                | Parameter                           | Value | Unit |

|-----------------------|-------------------------------------|-------|------|

| R <sub>thj-case</sub> | Thermal Resistance Junction to Case | 1.7   | °C/W |

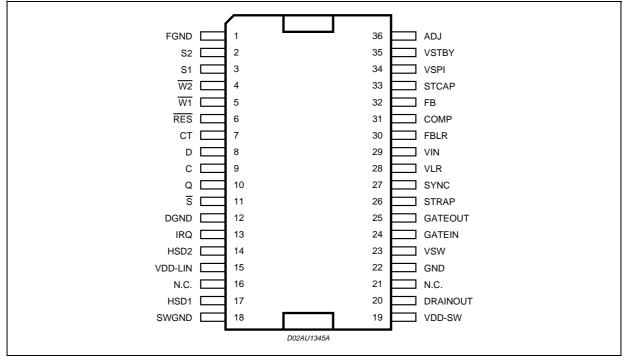

## **PIN CONNECTION**

## **PIN FUNCTION**

| Pin Number | Pin Name | Function                                      |

|------------|----------|-----------------------------------------------|

| 1          | FGND     | Analog Ground                                 |

| 2          | S2       | Input Voltage for LVW2                        |

| 3          | S1       | Input Voltage for LVW1                        |

| 4          | W2       | LVW2 Output                                   |

| 5          | W1       | LVW1 Output                                   |

| 6          | RES      | Reset                                         |

| 7          | СТ       | Timing capacitor                              |

| 8          | D        | SPI Serial Input                              |

| 9          | С        | SPI Clock                                     |

| 10         | Q        | SPI Serial Output                             |

| 11         | S        | SPI Chip Select                               |

| 12         | DGND     | SPI Ground                                    |

| 13         | IRQ      | Interrupt                                     |

| 14         | HSD2     | HSD2 Output                                   |

| 15         | VDD-LIN  | Battery                                       |

| 16         | N.C.     | Not Connected                                 |

| 17         | HSD1     | HSD1 Output                                   |

| 18         | SWGND    | Switching Ground                              |

| 19         | VDD-SW   | PWM Battery                                   |

| 20         | DRAINOUT | Drain of the exrternal MOS                    |

| 21         | N.C.     | Not Connected                                 |

| 22         | GND      | Ground                                        |

| 23         | VSW      | Source of the external MOS                    |

| 24         | GATEIN   | Gate of the internal MOS                      |

| 25         | GATEOUT  | Switching Output for power mos gate           |

| 26         | STRAP    | Bootstrap                                     |

| 27         | SYNC     | Synchronization                               |

| 28         | VLR      | REG2 Linear Voltage Regulator Output          |

| 29         | VIN      | REG2 Linear Voltage Regulator Input           |

| 30         | FBLR     | REG2 Linear Voltage Regulator Feedback        |

| 31         | COMP     | PWM Compensation                              |

| 32         | FB       | PWM Feedback                                  |

| 33         | STCAP    | ST-CAP                                        |

| 34         | VSPI     | Supply Voltage for SPI I/O                    |

| 35         | VSTBY    | REG1 Stand-by Linear Voltage Regulator Output |

| 36         | ADJ      | 3.3V/5V REG1 Voltage Select                   |

## ELECTRICAL CHARACTERISTCS

$(T_{amb} = 25^{\circ}C, V_{DD} = 14.4V)$

| Symbol                          | Parameter                                                              | Test Condition                                                                                          | Min.     | Тур.     | Max.     | Unit     |

|---------------------------------|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|----------|----------|----------|----------|

| I <sub>Q,STBY</sub>             | Quiescent current with regulators<br>and High-side drivers off         | W1, W2, RES, IRQ, not active;<br>REG2, HSD1, HSD2, PWM off;<br>S, C, D fixed at high/low logic<br>level |          |          | 100      | μA       |

| T <sub>sd</sub>                 | Thermal Shutdown Junction<br>Temperature                               |                                                                                                         |          | 150      |          | °C       |

| SMPS.PM<br>T <sub>amb</sub> = 2 | / <b>M</b><br>5°C, V <sub>DD</sub> = 14.4V, V <sub>o</sub> = 5V; unles | s otherwise specified.)                                                                                 | -1       | 1        |          |          |

| V <sub>o,min</sub>              | Minimum Output Voltage                                                 | l <sub>o</sub> = 200mA                                                                                  | 2.4      | 2.5      | 2.6      | V        |

| V <sub>o,max</sub>              | Maximum Output Voltage                                                 | l <sub>o</sub> = 200mA                                                                                  | 9.6      | 10       | 10.4     | V        |

| Vref,PWM                        | Voltage Reference                                                      |                                                                                                         |          | 1.275    |          | V        |

| Vi                              | Input Voltage Range                                                    | $V_0 = 5V; I_0 = 0.5A$                                                                                  | 6        |          | 18       | V        |

| $\Delta V_{o}$                  | Line Regulation                                                        | I <sub>o</sub> = 0.5A                                                                                   |          |          | 100      | mV       |

| $\Delta V_{0}$                  | Load Regulation                                                        | $V_0 = 5V; I_0 = 0.2A \text{ to } 0.5A$                                                                 |          |          | 50       | mV       |

| Vd                              | Dropout Voltage between Pin 19                                         | I <sub>o</sub> = 0.5A, V <sub>o</sub> = 5V                                                              |          |          | 0.5      | V        |

|                                 | and Pin 23                                                             | I <sub>o</sub> = 1A, V <sub>o</sub> = 5V                                                                |          |          | 1        | V        |

| I <sub>Lim</sub>                | Current Limit                                                          |                                                                                                         | 1.5      |          |          | Α        |

| η                               | Efficiency                                                             | $f = 260$ kHz; $I_0 = 0.5$ A<br>f = 400kHz; $I_0 = 0.5$ A                                               |          | 90<br>86 |          | %<br>%   |

| SVR                             | Supply Voltage Ripple Rejection                                        | $\begin{array}{l} \Delta V_i = 1 V rms; \\ f_{ripple} = 300 Hz; \ I_o = 0.4 A \end{array}$              |          | 50       |          | dB       |

| OSCILLA                         | TOR                                                                    |                                                                                                         |          |          |          |          |

| f <sub>1</sub>                  | Swiching frequency                                                     |                                                                                                         | 249      | 260      | 271      | kHz      |

| f <sub>2</sub>                  | Swiching frequency                                                     |                                                                                                         | 384      | 400      | 416      | kHz      |

| $\frac{\Delta f}{\Delta V_i}$   | Voltage Stability of Switching<br>Frequency                            | V <sub>DD</sub> = 8 to 18V                                                                              |          | Tbd      |          | %        |

| $rac{\Delta f}{\Delta T_j}$    | Temperature Stability of Switching<br>Frequency                        | T <sub>j</sub> = -40°C to 85°C                                                                          |          | Tbd      |          | %        |

| SYNC                            |                                                                        | <u> </u>                                                                                                | <u> </u> | 1        |          | <u> </u> |

| VIL                             | Low Input Voltage                                                      |                                                                                                         |          |          | 0.8      | V        |

| VIH                             | High Input Voltage                                                     |                                                                                                         | 2        |          | <u> </u> | V        |

| V <sub>OL</sub>                 | Low Output Voltage                                                     |                                                                                                         |          |          | 0.4      | V        |

| V <sub>OH</sub>                 | High Output Voltage                                                    | I <sub>SOURCE</sub> =1.5mA                                                                              | 4        |          |          | V        |

## ELECTRICAL CHARACTERISTCS (continued)

$(T_{amb} = 25^{\circ}C, V_{DD} = 14.4V)$

| Symbol                   | Parameter                              | Test Condition                                                                                                                                                                   | Min.        | Тур.         | Max.        | Unit   |

|--------------------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------|-------------|--------|

| I <sub>SLAVE</sub>       | Slave Sink Current                     |                                                                                                                                                                                  |             | 100          |             | μA     |

| TW                       | Output Pulse Width                     |                                                                                                                                                                                  |             | 300          |             | ns     |

| REG1 - 3.                | 3V/5V STBY LINEAR VOLTAGE R            | EGULATOR                                                                                                                                                                         |             | I            |             | I      |

| V <sub>STBY</sub>        | Output Voltage                         | no load; ADJ pin = open<br>no load; ADJ pin = VSTBY pin                                                                                                                          | 4.9<br>3.20 | 5<br>3.3     | 5.1<br>3.4  | V<br>V |

| $\Delta V_{\text{line}}$ | Line Regulation                        | no load; 7 < Vdd < 26V                                                                                                                                                           |             | 5            | 50          | mV     |

| $\Delta V_{\text{load}}$ | Load Regulation                        | 5mA < I <sub>o</sub> < 250mA                                                                                                                                                     |             | 12           | 80          | mV     |

| V <sub>dropout</sub>     | V <sub>STCAP</sub> - V <sub>STBY</sub> | $    I_o = 100 m A, V_o = 5 V \\     I_o = 100 m A, V_o = 3.3 V $                                                                                                                |             | 0.36<br>0.47 | 0.5<br>0.65 | V      |

| l <sub>lim</sub>         | Current Limit                          | Out short to GND                                                                                                                                                                 | 300         |              |             | mA     |

| SVR                      | Supply Voltage Rejection               | $\Delta V_{DD}$ = 1Vrms: f = 300Hz<br>I <sub>o</sub> = 250mA                                                                                                                     |             | 55           |             | dB     |

| REG2 - L                 | NEAR VOLTAGE REGULATOR 1.              | 5V to 3.3V                                                                                                                                                                       |             |              |             |        |

| $V_{LR}$                 | Linear Regulator Output Voltage        | no load; 4.75 $\le$ V <sub>IN</sub> $\le$ 16V; 1+ (R5/R6) = 2.588                                                                                                                | 3.2         | 3.3          | 3.4         | V      |

|                          |                                        | no load; $3.135 \le V_{IN} \le 16V$ ;<br>1+ (R5/R6) = 1.176                                                                                                                      | 1.45        | 1.5          | 1.55        |        |

| V <sub>IN</sub>          | Input Voltage                          | $I_O = 150mA$<br>1.5V $\leq V_{LR} \leq 2V$                                                                                                                                      | 3.135       |              | 16          | V      |

|                          |                                        | $I_O = 300mA$<br>1.5V $\leq V_{LR} \leq 3.3V$                                                                                                                                    | 4.75        |              | 16          | V      |

| $\Delta V_{\text{load}}$ | Load Regulation                        | $\begin{array}{l} 5mA \leq I_O \leq 300mA \\ 4.75V \leq V_{IN} \leq 16V; \ 1.5V \leq V_{LR} \leq 3.3V \end{array}$                                                               |             | 12           |             | mV     |

| $\Delta V_{\text{line}}$ | Line Regulation                        | no load;<br>4.75V $\leq$ V_{IN} $\leq$ 16V; 1.5V $\leq$ V_{LR} $\leq$ 3.3V                                                                                                       |             | 1            |             | mV     |

| V <sub>ref,REG2</sub>    | Voltage Reference                      |                                                                                                                                                                                  |             | 1.275        |             | V      |

| I <sub>Lim</sub>         | Current Limit                          | Out Short to ground                                                                                                                                                              | 400         |              |             | mA     |

| SVR                      | Supply Voltage Rejection               | $\label{eq:VIN} \begin{array}{l} V_{\text{IN}} = 5 V dc, \ 0.5 V acpp, \ 300 Hz \\ I_O = 300 mA; \ 1.5 V \leq V_{LR} \leq 3.3 V \end{array}$                                     |             | 55           |             | dB     |

|                          |                                        | $\label{eq:VIN} \begin{array}{l} V_{IN}=3.3 \text{Vdc}, \ 0.5 \text{Vacpp}, \ 300 \text{Hz} \\ I_O=150 \text{mA}; \ 1.5 \text{V} \leq \text{V}_{LR} \leq 2 \text{V} \end{array}$ |             | 55           |             | dB     |

| HSD1                     |                                        |                                                                                                                                                                                  |             | •            |             | •      |

| V <sub>sat, peak</sub>   | Saturation Voltage                     | I <sub>O</sub> = 0.5A                                                                                                                                                            |             |              | 250         | mV     |

| l <sub>lim</sub>         | Current Limit                          |                                                                                                                                                                                  | 600         |              |             | mA     |

| Lload                    | Load Inductance                        |                                                                                                                                                                                  |             |              | 100         | mH     |

## ELECTRICAL CHARACTERISTCS (continued)

$(T_{amb} = 25^{\circ}C, V_{DD} = 14.4V)$

| Symbol                 | Parameter                                                 | Test Condition                      | Min.  | Тур.                        | Max.  | Unit |

|------------------------|-----------------------------------------------------------|-------------------------------------|-------|-----------------------------|-------|------|

| HSD2                   | L                                                         | 1                                   | I     | 1                           |       | L    |

| V <sub>sat, peak</sub> | Saturation Voltage                                        | I <sub>O</sub> = 0.2A               |       |                             | 250   | mV   |

| l <sub>lim</sub>       | Current Limit                                             |                                     | 300   |                             |       | mA   |

| L <sub>load</sub>      | Load Inductance                                           |                                     |       |                             | 100   | mH   |

| VOLTAGE                | WARNING                                                   |                                     |       |                             |       |      |

| V <sub>st</sub>        | Sense Low Threshold                                       |                                     | 1.245 | 1.275                       | 1.305 | V    |

| V <sub>sth</sub>       | Sense Threshold Hysteresis                                |                                     | 35    | 45                          | 60    | mV   |

| V <sub>SL</sub>        | Sense Output Low Voltage                                  | I <sub>o</sub> = 1mA                |       |                             | 0.4   | V    |

| I <sub>SH</sub>        | Sense Output Leakage                                      | $V_W = 5V; V_{SI} \ge 1.5V$         |       |                             | 10    | μA   |

| I <sub>SI</sub>        | Sense Input Current                                       | V <sub>SI</sub> =5V                 |       | 1                           |       | μA   |

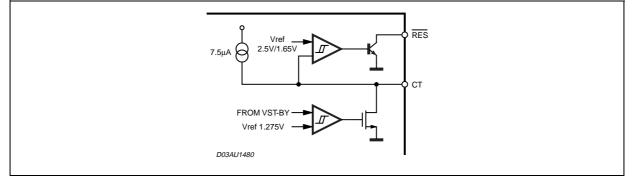

| RESET                  |                                                           |                                     |       |                             |       |      |

| V <sub>RT</sub>        | Reset Threshold Voltage                                   |                                     |       | 0.95 х<br>V <sub>STBY</sub> |       | V    |

| V <sub>RTH</sub>       | Reset Threhold Hysteresis                                 |                                     |       | 0.02 х<br>V <sub>STBY</sub> |       | V    |

| V <sub>RL</sub>        | Reset Output Voltage                                      | I <sub>o</sub> = 1mA                |       |                             | 0.4   | V    |

| I <sub>RH</sub>        | Reset Output Leakage                                      | V <sub>RT</sub> = V <sub>STBY</sub> |       |                             | 10    | μΑ   |

| V <sub>CTth</sub>      | Delay Comparator Threshold                                |                                     |       | 0.5 x<br>V <sub>STBY</sub>  |       |      |

| $V_{CThy}$             | Delay Comparator Threshold<br>Hysteresys                  |                                     |       | 180                         |       | mV   |

| I <sub>CT1</sub>       | Timing Capacitor Output Source<br>Current                 |                                     |       | 7.5                         |       | μΑ   |

| R <sub>CT2</sub>       | Timing Capacitor Output Pull-<br>Down equivalent Resistor |                                     |       | 150                         |       | Ω    |

| JIAGNOS                | TIC PARAMETERS                                            | -                                   |       |                             |       |      |

| Symbol                 | Parameter                                                 | Test Condition                      | Min.  | Тур.                        | Max.  | Unit |

| HSD1W1                 | High Side Driver 1 Overcurrent                            |                                     |       | 0.95                        |       | А    |

| HSD1W1         | High Side Driver 1 Overcurrent<br>Warning activation                        |                                                                      | 0.95 | A |

|----------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------|------|---|

| HSD1W2         | High Side Driver 1 Open Load<br>Warning activation                          | HSD1 output voltage in test mode                                     | 3    | V |

| HSD1W2<br>TEST | High Side Driver 1 V <sub>DD</sub> Short<br>Warning activation in test mode | HSD1 in test mode<br>Measure V <sub>VDD-LIN</sub> -V <sub>HSD1</sub> | 1.5  | V |

| HSD2W1         | High Side Driver 2 Overcurrent<br>Warning activation                        |                                                                      | 0.7  | A |

| Symbol     | Parameter                                                                   | Test Condition                                                       | Min. | Тур. | Max. | Unit |

|------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------|------|------|------|------|

| HSD2W2     | High Side Driver 2 Open Load<br>Warning activation                          | HSD2 output voltage in test mode                                     |      | 3    |      | V    |

| HSD2W3     | High Side Driver 2 V <sub>DD</sub> Short<br>Warning activation in test mode | HSD2 in test mode<br>Measure V <sub>VDD-LIN</sub> -V <sub>HSD1</sub> |      | 1.5  |      | V    |

| THW        | Thermal warning activation                                                  |                                                                      |      | 145  |      | °C   |

| IRQ - Inte | rrupt Request Pin                                                           |                                                                      |      | L    |      |      |

| IRQ-L      | IRQ Low voltage                                                             | I <sub>o</sub> = 1mA                                                 |      |      | 0.4  | V    |

| IRQ-H      | IRQ Leakage                                                                 | V <sub>irq</sub> = 5V                                                |      |      | 1    | μΑ   |

## SPI INTERFACE

| Symbol            | Alt              | Parameter                                                   | Test Conditions        | Min.                | Max.                | Unit |

|-------------------|------------------|-------------------------------------------------------------|------------------------|---------------------|---------------------|------|

| Recomme           | ended DC         | Operating Voltage                                           | 1                      | I                   |                     |      |

| V <sub>SPI</sub>  |                  | Supply Voltage for SPI I/O                                  |                        | 3                   | 5.5                 | V    |

| Input Para        | ameters (        | Tamb = 25°C, f = 1MHz)                                      |                        |                     |                     |      |

| C <sub>IN</sub>   |                  | Input Capacitance (D)                                       |                        |                     | 8                   | pF   |

| C <sub>IN</sub>   |                  | Input Capacitance (others pins)                             |                        |                     | 6                   | pF   |

| t <sub>LPF</sub>  |                  | Input Signal Pulse Width                                    |                        |                     | 10                  | ns   |

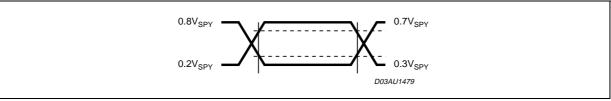

| DC Chara          | cteristics       | (T <sub>amb</sub> = -40 to 85°C, V <sub>SPI</sub> = 3V to 5 | 5.5V)                  |                     |                     |      |

| lLI               |                  | Input Leakage Current                                       |                        |                     | 2                   | μΑ   |

| I <sub>LO</sub>   |                  | Output Leakage Current                                      |                        |                     | ±2                  | μΑ   |

| VIL               |                  | Input Low Voltage                                           |                        | -0.3                | 0.3V <sub>SPI</sub> | V    |

| VIH               |                  | Input High Voltage                                          |                        | 0.7V <sub>SPI</sub> | V <sub>SPI</sub> +1 | V    |

| V <sub>OL</sub>   |                  | Output Low Voltage                                          | I <sub>OL</sub> = 2mA  |                     | 0.2V <sub>SPI</sub> | V    |

| V <sub>OH</sub>   |                  | Output High Voltage                                         | I <sub>OH</sub> = -2mA | 0.8V <sub>SPI</sub> |                     | V    |

| AC Chara          | cteristics       | ; (Tamb = -40 to 85°C, V <sub>SPI</sub> = 3V to 5           | 5.5V                   |                     |                     |      |

| tSCLH             | ts∪              | S Setup Time                                                |                        | 50                  |                     | ns   |

| tCLSH             | t <sub>SH</sub>  | S Hold Time                                                 |                        | 50                  |                     | ns   |

| t <sub>CH</sub>   | t <sub>WH</sub>  | Clock High Time                                             |                        | 200                 |                     | ns   |

| t <sub>CL</sub>   | t <sub>WL</sub>  | Clock Low Time                                              |                        | 300                 |                     | ns   |

| t <sub>CLCH</sub> | t <sub>RC</sub>  | Clock Rise Time                                             |                        |                     | 1                   | μs   |

| t <sub>CHCL</sub> | t <sub>FC</sub>  | Clock Fall Time                                             |                        |                     | 1                   | μs   |

| t <sub>DVCH</sub> | t <sub>DSU</sub> | Data In Setup Time                                          |                        | 50                  |                     | ns   |

| t <sub>CHDX</sub> | t <sub>DH</sub>  | Data In Hold Time                                           |                        | 50                  |                     | ns   |

| t <sub>DLDH</sub> | t <sub>RI</sub>  | Data In Rise Time                                           |                        |                     | 1                   | μs   |

|                   |                  |                                                             |                        | 1                   | 1                   |      |

## L5953

| Symbol            | Alt              | Parameter                 | Test Conditions                                                | Min.       | Max. | Unit     |

|-------------------|------------------|---------------------------|----------------------------------------------------------------|------------|------|----------|

| t <sub>DHDL</sub> | tFI              | Data in Fall Time         |                                                                |            | 1    | μs       |

| tSHSL             | t <sub>CS</sub>  | S Deselect Time           | 4.5V < V <sub>SPI</sub> < 5.5V<br>3V < V <sub>SPI</sub> < 4.5V | 200<br>250 |      | ns<br>ns |

| t <sub>SHQZ</sub> | t <sub>DIS</sub> | Output Disable Time       |                                                                |            | 150  | ns       |

| t <sub>QVCL</sub> | t <sub>V</sub>   | Clock Low to Output Valid |                                                                |            | 250  | ns       |

| t <sub>CLQX</sub> | t <sub>HO</sub>  | Output Hold Time          |                                                                | 0          |      | ns       |

| t <sub>QLQH</sub> | t <sub>RO</sub>  | Output Rise Time          |                                                                |            | 100  | ns       |

| t <sub>QHQL</sub> | t <sub>FO</sub>  | Output Fall Time          |                                                                |            | 100  | ns       |

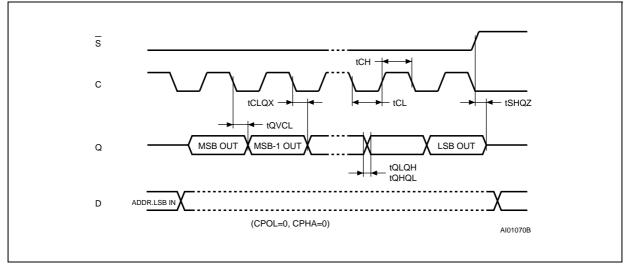

## Figure 1. AC Testing Input Output WaveformsI

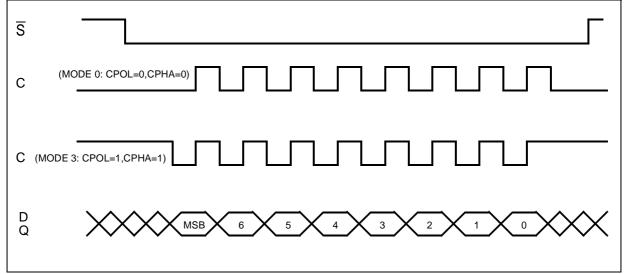

## Figure 2. SPI Clocking Scheme

**A7/**

## Figure 3. Output Timing

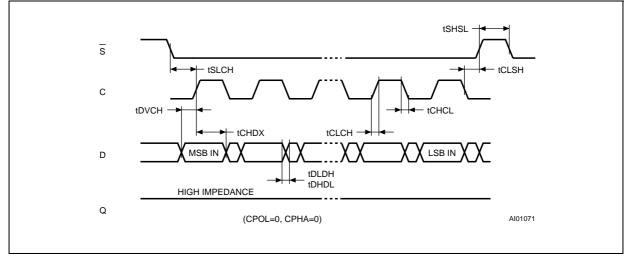

## Figure 4. Serial Input Timing

## FUNCTIONAL DESCRIPTION

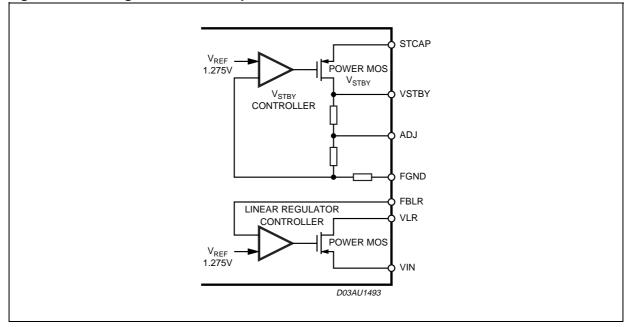

## **REG1 Stand-by Regulator (Figure 5)**

The stand-by regulator output voltage can be 5V or 3.3V. It is externally selectable by means of the ADJ pin:

- leaving the ADJ pin open, the output voltage is 5V;

- connecting the ADJ pin to the Vstby pin the output voltage becomes 3.3V.

This regulator is supplied by STCAP pin and provide the reset information.

It has a current protection which limits the maximum allowable output current.

## Reset (Figure 6)

The  $\overline{\text{RES}}$  pin is an open collector that is activated (that is forced to zero) when the stand-by regulator is not in regulation (including thermal shutdown and faults). The indication that REG1 is in regulation is delayed by a time

set up by the external capacitor CT.

When the  $\overline{\text{RES}}$  is switched on, HSD1, HSD2, REG2, PWM are turned off and until the  $\overline{\text{RES}}$  is forced to zero only the REG1 and low Voltage Warnings are active.

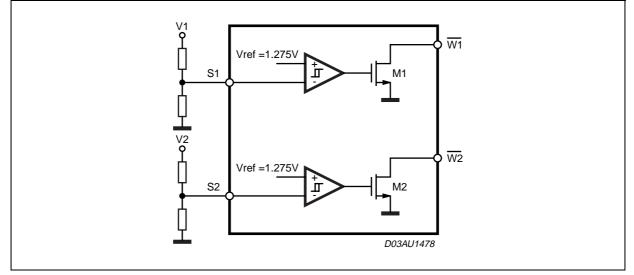

## Low Voltage Warning(Figure 7)

This circuit is able to sense two different voltages through external resistors to increase the overall flexibility.

If S1 pin voltage is higher than Vst, the output mos M1 is off:  $\overline{W1}$  is floating and can be pulled up by an external resistor. If S1 pin voltage goes down and becomes lower than Vst, the mos M1 is turned on and forces  $\overline{W1}$  to zero. The same thing happens for S2 -  $\overline{W2}$ .

The outputs  $\overline{W1}$  and  $\overline{W2}$  can be connected together to get a single output.

## **REG2 Linear Voltage Regulator (Figure 5)**

REG2 is a linear voltage regulator with a dedicated supply pin VIN. The output voltage (between 1.5V and 3.3V) is fixed by an external divider. It can be turned on/off by SPI. It has a current protection which limits the maximum allowable output current.

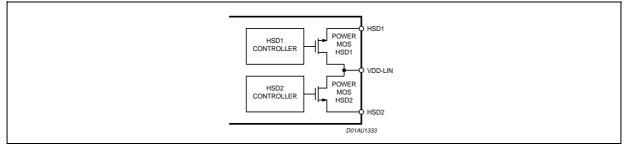

## High Side Drivers (Figure 8)

Two high-side driver with charge pump controlled by SPI are available inside L5953. They are protected against short to ground: the short circuit potection limits the maximum output current.

A diagnostic procedure is available to detect open load, short to battery and overcurrent.

Open load and short to battery can be reveal only in test mode while overcurrent is active only during normal operation of the device. (see OPERATION -page 13

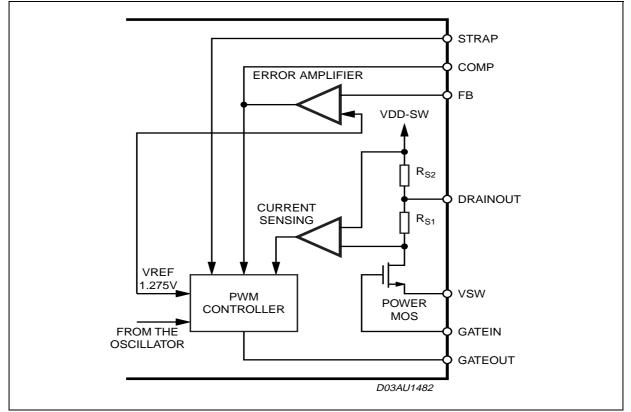

## PWM Step Down Voltage Regulator (Figure 9)

The switching regulator inside the L5953 is a voltage control mode (also known as "direct duty cycle") Buck regulator: the error signal coming from the error amplifier is compared with a sawtooth to set on and off times of the power switch.

The feedforward control is introduced to get a quickly response to input voltage changes: the sawtooh has a fixed frequency and an amplitude variable with the battery voltage.

Continuous mode operation is recommended in order to reduce the stress of the output capacitor and of the free-wheeling diode.

#### Error amplifier and compensation network

The error amplifier (EA) is a voltage amplifier whose non-inverting input is fixed to the reference voltage (1.275V bandgap voltage) and whose inverting input and output are externally available for feedback and frequency compensation.

## Figure 5. Linear regulators - Internal pin connections

## Figure 6. Reset Internal pin Connection

## Figure 7. Low Voltage Warning Block Diagram.

## Figure 8. HSD - Internal pin connections

Figure 9. PWM - Internal pin connections

## SPI INTERFACE

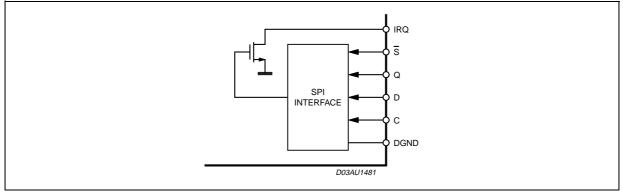

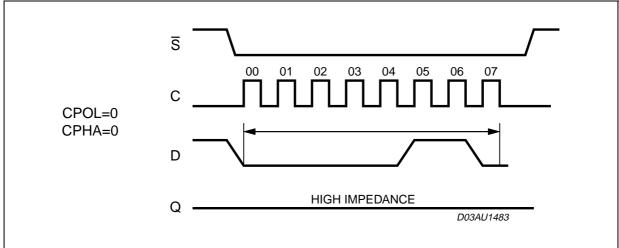

## Signals Description (Figure 10)

The SPI interface available inside L5953 is able to work both in Mode 0 and Mode 3.

Serial Output (Q). The output pin is used to transfer data serially out of the L5953. Data is shifted out on the falling edge of the serial clock.

Serial Input (D). The input pin is used to transfer data serially into the device. It receives instructions, addresses, and data to be written. Input is latched on the rising edge of the serial clock.

Serial Clock (C). The serial clock provides the timing of the serial interface. Instructions, addresses, or data present at the input pin are latched on the rising edge of the clock input, while data on the Q pin changes after the falling edge of the clock input.

**Chip Select** ( $\overline{S}$ ). This input is used to select the L5953. The chip is selected by a high to low transition on the  $\overline{S}$  pin. At any time, the chip is deselected by a low to high transition on the  $\overline{S}$  pin. As soon as the chip is deselected, the Q pin is at high impedance state. The pin allows multiple L5953 to share the same SPI bus. After power up, the chip is at the deselect state.

SPI Input/Output are supplied by an external supply voltage VSPI while the core is supplied by the stand-by regulator VSTBY. The SPI is resetted by an internal signal whose buffered version is RES.

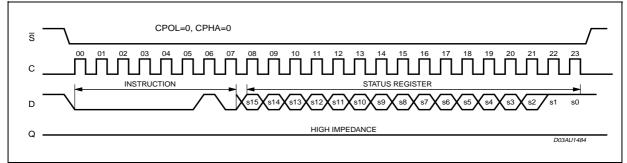

#### OPERATIONS

All instructions, addresses and data are shifted in and out of the chip MSB first. Data input (D) is sampled on the first rising edge of clock (C) after the chip select  $(\overline{S})$  goes low. Prior to any operation, a one-byte instruction code must be entered in the chip. This code is entered in the chip. This code is entered via the data input (D), and latched on the rising edge of the clock input (C). To enter an instruction code, the product must have been previously selected ( $\overline{S} =$  low). Table 1 shows the instruction set and format for device operation. An invalid instruction (one not contained in table 1) leaves the chip as previously selected.

#### Write Enable (WREN and Write Disable (WRDI)

The L5953 contains a write enable latch. This latch must be set prior to every WRITE operation. The WREN instruction will set the latch and the WRDI istruction will reset the latch. The latch is reset under all the following conditions:

- Power on

- WRDI instruction executed

As soon as the WREN or WRDI instruction is received by the L5953, the circuit executes the instruction and enters a wait mode until it is deselected.

| Instruction | Description              | Instruction Format |  |  |

|-------------|--------------------------|--------------------|--|--|

| WREN        | Set Write Enable Latch   | 00000110           |  |  |

| WRDI        | Reset Write Enable Latch | 00000100           |  |  |

| WSTA        | Write Status Register    | 00000010           |  |  |

| RDIA        | Read Diagnostic Register | 00000101           |  |  |

| RSTA        | Read Status Register     | 00000011           |  |  |

#### Table 1. Instruction Set.

## L5953

## Table 2. Status Register.

| s15  | s14  | s13  | s12 | s11 | s10          | s9  | s8  | s7  | s6  | s5  | s4  | s3  | s2  | s1 | s0            |

|------|------|------|-----|-----|--------------|-----|-----|-----|-----|-----|-----|-----|-----|----|---------------|

| REG2 | HSD1 | HSD2 | TBD | TBD | PWM<br>Freq. | PWM | TBD |    | START<br>DIAG |

## **Table 3. Status Register Description**

|     |                                              | 0              | 1                                                                                                                                                                      |

|-----|----------------------------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| s15 | REG2 Linear Voltage<br>Regulator 1.5 to 3.3V | Regulator off  | Regulator on                                                                                                                                                           |

| s14 | High Side Driver 1                           | HSD1 off       | HSD1 on                                                                                                                                                                |

| s13 | High Side Driver 2                           | HSD2 off       | HSD2 on                                                                                                                                                                |

| s12 | TBD                                          |                |                                                                                                                                                                        |

| s11 | TBD                                          |                |                                                                                                                                                                        |

| s10 | PWM switching frequency                      | 260kHz         | 400kHz                                                                                                                                                                 |

| s9  | PWM Voltage Regulator                        | PWM1 off       | PWM1 on                                                                                                                                                                |

| s8  | TBD                                          |                |                                                                                                                                                                        |

| s7  | TBD                                          |                |                                                                                                                                                                        |

| s6  | TBD                                          |                |                                                                                                                                                                        |

| s5  | TBD                                          |                |                                                                                                                                                                        |

| s4  | TBD                                          |                |                                                                                                                                                                        |

| s3  | TBD                                          |                |                                                                                                                                                                        |

| s2  | TBD                                          |                |                                                                                                                                                                        |

| s1  | Test Mode                                    | Test Mode off  | Test Mode on<br>NOTE: in this case the bits s15 - s2 are internally<br>set to 0 (regulators and high side drivers are in off<br>condition)                             |

| s0  | Diagnostic                                   | Diagnostic off | Starts the diagnostic procedure:<br>- in Test Mode if s1=1;<br>- during normal operation if s1=0<br>If s1=0 and s0=1, must be s14 = 1 (HSD1 ON)<br>and s13=1 (HSD2 ON) |

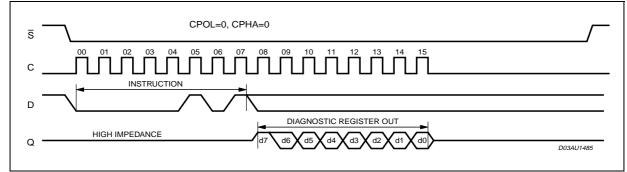

## Table 4. Diagnostic Register.

| d7        | d6     | d5     | d4     | d3     | d2     | d1     | d0  |

|-----------|--------|--------|--------|--------|--------|--------|-----|

| Test mode | HSD1W1 | HSD1W2 | HSD1W3 | HSD2W1 | HSD2W2 | HSD2W3 | THW |

|    |                 | 0                                                                                                       | 1                                                                                          |

|----|-----------------|---------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| d7 | Test mode       | The Diagnostic Register is<br>referred to a test performed<br>during the normal working<br>of the L5953 | The Diagnostic Register is referred to a test performed in Test mode                       |

| d6 | HSD1W1          | If d7=0: HSD1 in normal<br>condition;<br>If d7=1: bit value<br>meaningless                              | If d7=0: HSD1 is in<br>overcurrent<br>If d7=1: bit value<br>meaningless                    |

| d5 | HSD1W2          | If d7=0: bit value<br>meaningless;<br>If d7=1: HSD1 in normal<br>condition                              | If d7=0: bit value<br>meaningless<br>If d7=1: an open load is<br>present on HSD1           |

| d4 | HSD1W3          | If d7=0: bit value<br>meaningless;<br>If d7=1: HSD1 in normal<br>condition                              | If d7=0: bit value<br>meaningless<br>If d7=1: HSD1 is shorted to<br>the supply voltage VDD |

| d3 | HSD2W1          | If d7=0: HSD1 in normal<br>condition;<br>If d7=1: bit value<br>meaningless                              | If d7=0: HSD2 is in<br>overcurrent;<br>If d7=1: bit value<br>meaningless                   |

| d2 | HSD2W2          | If d7=0: bit value<br>meaningless<br>If d7=1: HSD2 in normal<br>condition                               | If d7=0: bit value<br>meaningless<br>If d7=1: an open load is<br>present on HSD2           |

| d1 | HSD1W3          | If d7=0: bit value<br>meaningless<br>If d7=1: HSD2 in normal<br>condition;                              | If d7=0: bit value<br>meaningless<br>If d7=1: HSD1 is shorted to<br>the supply voltage VDD |

| d0 | Thermal Warning | Normal condition                                                                                        | Overtemperature protection<br>activated(Tj>150°C)                                          |

### Table 5. Diagnostic Register Description.

## SUMMARY OF THE MAIN OPERATIONS

## **Operation A**

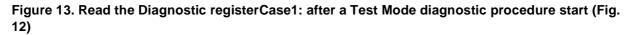

- Test Mode Diagnostic Procedure Start

- 1) WREN instruction (Fig.11)

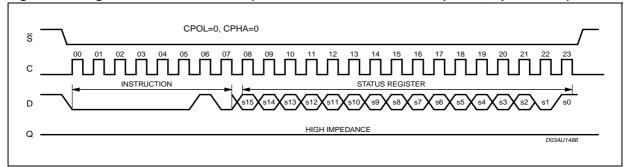

- 2) WSTA instruction (Fig.12)

## **Operation B**

- Read the Diagnostic Register

Case1: after a Test Mode Diagnostic Procedure Start

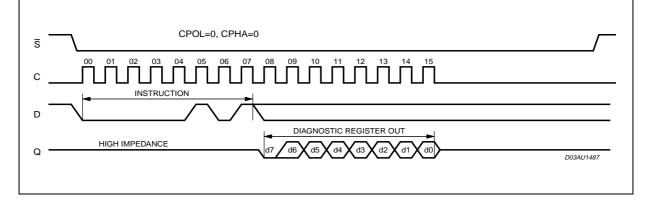

1) RDIA instruction (Fig.13)

2) Diagnostic Pagister system (Fig.12)

- 2) Diagnostic Register output (Fig.13)

- NOTE: an operation B must follow an operation A. The delay between the end of the operations A to the start of the operations B must be longer than 100µS

## **Operation C**

Write the Status Register

- 1) WREN instruction (Fig.11)

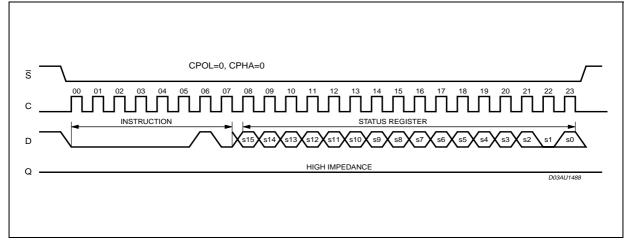

- 2) WSTA instruction (Fig.16)

## **Operation D**

- Read the Status Register

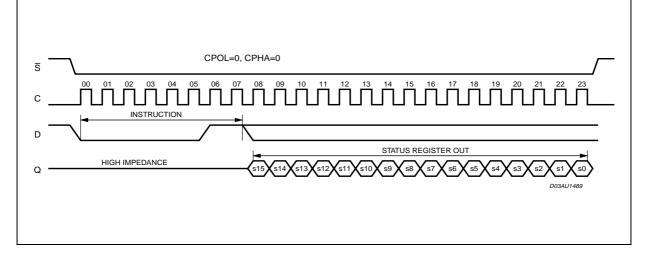

- 1) RSTA instruction (Fig.17)

- 2) Status Register output (Fig.17)

## **Operation E**

- Diagnostic Procedure Start

1) WREN instruction (Fig.11)

- 2) WSTA instruction (Fig.14)

## **Operation F**

- Read the Diagnostic Register

- Case 2: after a Diagnostic Procedure Start

- 1) RDIA instruction (Fig.15)

- 2) Diagnostic Register output (Fig.15)

An operation F must follow an operation E if the pin IRQ is not activated.

The delay between the Operation E and an Operation F must be longer than  $100\mu$ s. To be recognized, the fault must be present without interruptions during all the delay above mentionned. After an Operation F, the bit s0 of the Status Register is resettled (0)

## **Operation G**

- Write operation disabled

- 1) WRDI instruction (Table 1)

## **Operation H**

- Read the Diagnostic Register case 3: after an IRQ pin activation

- 1) RDIA instruction (Fig. 15)

- 2) Diagnostic Register Output (Fig. 15)

The delay between the IRQ activation and an Operation F must be longer than  $100\mu s$

## Figure 11. Write Enable Latch Sequence

**A7**

Figure 14. Diagnostic Procedure Start (after a Write Enable Latch Sequence, operation A)

Figure 15. Read the Diagnostic RegisterCase2: during the normal working of the L5953 (after a Diagnostic Procedure Start, Fig.14)

57

17/24

## Figure 16. Write the Status Register (after a Write Enable Latch Sequence, operation A)

## Figure 17. Read the Status Register

## **IRQ - Interrupt Request Pin**

- It is an open drain pin activated (low) every time a variation occurs in the Diagnostic Register.

- Purpose: to alert the μP that one or more warning bit of the Diagnostic Register has changed from 0 to 1 or from 1 to 0.

- An activation of this pin puts the bit s0 of the Status Register to 1 (START DIAGNOSTIC) like an Operation E (Diagnostic Procedure Start). Then an Operation F has to be executed without an Operation E before.

- After an Operation F, the IRQ pin is disactivated, and goes to 1 if connected to a pull-up resistor.

## L5953 - Application Note

Figure 18. Block and Application Diagram

Figure 19. Block Diagram And Application With External Power MOS

57

19/24

PART LIST on Evaluation Board

| C1 = 470 μF              | C2 = 220 nF                                | C3 = 470 μF              | C4 = 10 μF  | C5 = 1 μF    | C6 = 100 nF |

|--------------------------|--------------------------------------------|--------------------------|-------------|--------------|-------------|

| C7 = 470 μF<br>ESR=65 mΩ | C8 = 56nF                                  | C9 = 2.7 nF              | C10 = 10 μF | C11 = 4.7 nF |             |

| R1 = 2.2 kΩ              | $R2 = 2 \times 1.5 k\Omega$<br>in parallel | R3 = 10 kΩ               | R4 = 220 kΩ | R5 = 3.3 kΩ  | R6 = 1 kΩ   |

| L1 = 180 μH              |                                            | D1 = 1N4007 or<br>MBR160 | D2 = MBR360 |              |             |

## **REG1 OUTPUT VOLTAGE**

$V_{STBY}$  = 5V if pin ADJ left floating  $V_{STBY}$  = 3.3V if pin ADJ is conneted to the pin  $V_{STBY}$

## **Timing Capacitor**

The value for this capacitor has to be chosen according the wanted power-on delay T<sub>d</sub>:

$$C11 = \frac{I_{CT1} \cdot T_{d}}{(0.5 \cdot V_{STBY}) + V_{CTLRY}}$$

where I<sub>CT1</sub> is the source current used to charge the timing capacitor and V<sub>STBY</sub> is the REG1 output voltage.

## Feedback resistors for REG2

$$R5 = R6 \cdot \left(\frac{V_{LR}}{V_{ref, REG2}}\right) - 1$$

where VLR is the required output voltage for REG2.

## External components for PWM regulator

## Bootstrap capacitor

The suggested value for the bootstrap capacitor is C6 = 100nF

Here following you find the criteria for the selection of the inductor L1, the free-wheeling diode D2, the output filter capacitor C7, the feedback resistor R1, R2 and the compensation network R3, C8, R4, C9 to have a Buck regulator working in Continuous mode. Continuous mode operation is recommended in order to reduce the stress of the output capacitor and of the free-wheeling diode.

## Inductor Selection

The minimum value of the inductor L7 has to be so that the maximum inductor current ripple  $\Delta I_{L,max}$  is 20% to 30% of the maximum load current load  $I_{o,max}$ . The maximum ripple is present when the switching frequency is minimum ( $f_{sw,min}$ ) and the input voltage is maximum ( $V_{in,max}$ ) so the minimum value for the inductor  $L_{min}$  is :

$$L_{min} = \frac{V_O}{\Delta I_{L, max}} \cdot 1 - \frac{V_O}{V_{i, max}} \cdot \frac{1}{f_{sw, min}}$$

## **Output Capacitor Selection**

The criteria for the selection of the capacitor C7 is based on the output voltage ripple requirements. The ripple on the output voltage is due to a capacitive contribute, often negligible, equal to

$$\Delta V_{c} = \frac{\Delta I_{L, \max}}{8 \cdot C7 \cdot f_{sw, \min}}$$

and a resistive contribute given by the ESR of the capacitor and which is equal to

$$\Delta V_{ESR} = ESR \cdot \Delta I_{L, max}$$

$\Delta$ VC fixes the value for C7 while  $\Delta$ VESR limits the ESR of the capacitor.Usually the capacitor is chosen so that the total ripple on the output regulated voltage Vo is equal to 1% of the value of Vo. If V<sub>ripple</sub> is the maximum allowed voltage ripple on Vo then it should result:

$$V_{ripple} \ge \sqrt{\Delta V_c^2 + \Delta V_{ESR}^2}$$

More often the minimum value of C7 is imposed by other considerations such as to get a good dynamic behaviour of the output voltage in case of large load variations.

#### Free-wheeling diode

The diode must withstand an average current Id equal to  $Id = I_{lim} (1 - D_{min})$

where  $I_{lim}$  is the current of intervention of the short circuit protection and  $D_{min}$  is the minimum duty cycle. As  $D_{min}$  is vey low, the current Id can be assumed equal to  $I_{lim}$ .

#### Compensation Network

In continuous mode, the voltage controlled buck converter showes two poles due to the output LC filter and one zero due to the ESR of the output capacitor. The suggested compensation network introduces two zeros and two poles:

- the zeros compensate the double poles of the LC filter

- one pole compensates the zero due to ESR of the output capacitor

- the second pole is nominally located in the origin which means an infinite gain at frequency null. In the reality the DC value of the closed loop gain can not be greater than the DC value of the EA open loop gain and the pole is located at very low frequency.

The values for the components of the compensation network can be fixed when the inductor L1 and the output capacitor C7 are chosen.

The necessary steps are following:

1.fix the cross-over frequency f<sub>C</sub> of the overall loop gain.

Usually

$$f_c = 0.1 \cdot f_{sw.min}$$

where  $f_{\text{sw,min}}$  is the minimum switching frequency

2.Calculate the high frequency error amplifier gain

$$G_{c} = 0.25 \cdot f_{c} \cdot 2 \cdot \pi \cdot \frac{L1}{ESR}$$

3. Chose R3 and calculate

$$C8 = 2 \cdot \frac{\sqrt{L1 \cdot C7}}{R3}$$

The value for R3 has not to be very high (for example  $10K\Omega$ ) so to limit the error due to an error amplifier input offset current.

4.Calculate

$$\begin{split} R_{p} &= \frac{R3}{\left(\frac{2}{ESR} \cdot \sqrt{\frac{L1}{C7}}\right) - 1} \\ RA &= R_{p} \cdot \frac{V_{O}}{V_{ref, PWM}} \\ R2 &= \frac{R_{p}}{1 - \frac{V_{ref, PWM}}{V_{O}}} \end{split}$$

5. Finally calculate

$$R4 = G_{C} \cdot R1$$

and

$$C9 = 2 \cdot \frac{\sqrt{L1 \cdot C7}}{R4}$$

22/24

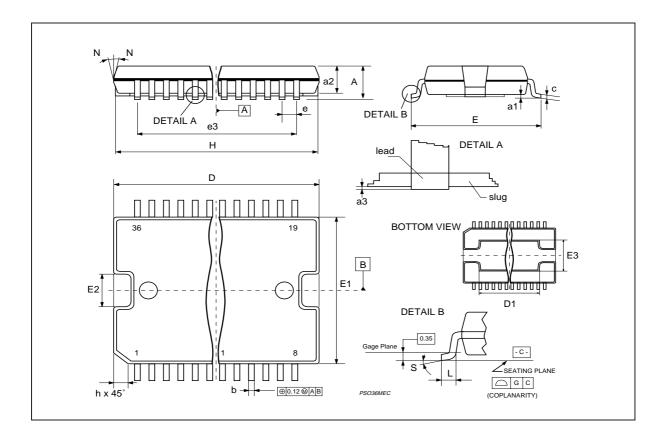

| DIM.   |           | mm    |       | inch  |        |       |  |  |

|--------|-----------|-------|-------|-------|--------|-------|--|--|

| DIN.   | MIN.      | TYP.  | MAX.  | MIN.  | TYP.   | MAX.  |  |  |

| Α      |           |       | 3.60  |       |        | 0.141 |  |  |

| a1     | 0.10      |       | 0.30  | 0.004 |        | 0.012 |  |  |

| a2     |           |       | 3.30  |       |        | 0.130 |  |  |

| a3     | 0         |       | 0.10  | 0     |        | 0.004 |  |  |

| b      | 0.22      |       | 0.38  | 0.008 |        | 0.015 |  |  |

| с      | 0.23      |       | 0.32  | 0.009 |        | 0.012 |  |  |

| D (1)  | 15.80     |       | 16.00 | 0.622 |        | 0.630 |  |  |

| D1     | 9.40      |       | 9.80  | 0.370 |        | 0.385 |  |  |

| Е      | 13.90     |       | 14.50 | 0.547 |        | 0.570 |  |  |

| е      |           | 0.65  |       |       | 0.0256 |       |  |  |

| e3     |           | 11.05 |       |       | 0.435  |       |  |  |

| E1 (1) | 10.90     |       | 11.10 | 0.429 |        | 0.437 |  |  |

| E2     |           |       | 2.90  |       |        | 0.114 |  |  |

| E3     | 5.80      |       | 6.20  | 0.228 |        | 0.244 |  |  |

| E4     | 2.90      |       | 3.20  | 0.114 |        | 0.126 |  |  |

| G      | 0         |       | 0.10  | 0     |        | 0.004 |  |  |

| Н      | 15.50     |       | 15.90 | 0.610 |        | 0.626 |  |  |

| h      |           |       | 1.10  |       |        | 0.043 |  |  |

| L      | 0.80      |       | 1.10  | 0.031 |        | 0.043 |  |  |

| N      |           |       | 10°(r | nax.) |        |       |  |  |

| S      | 8 °(max.) |       |       |       |        |       |  |  |

(1): "D" and "E1" do not include mold flash or protrusions

Mold flash or protrusions shall not exceed 0.15mm (0.006 inch)

Critical dimensions are "a3", "E" and "G".

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners

© 2003 STMicroelectronics - All rights reserved

#### STMicroelectronics GROUP OF COMPANIES

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States

www.st.com